Portas Lógicas e Tecnologias TTL e CMOS

Portas Lógicas

Uma Porta Lógica Digital é um dispositivo eletrônico que implementa funções lógicas (booleanas) e toma decisões baseado em diferentes combinações de níveis lógicos digitais (0 e 1) aplicados às suas entradas.

Uma porta lógica pode ter uma ou mais entradas, dependendo do circuito lógico que é implementado, e no geral somente possui uma saída digital. Podemos conectar e combinar diversas portas lógicas para obter circuitos ou funções lógicas adicionais, como circuitos combinacionais ou sequenciais.

As portas lógicas podem ser obtidas comercialmente na forma de circuitos integrados, que estão disponíveis em duas tecnologias ou famílias básicas, a tecnologia TTL (Transistor-Transistor Logic / Lógica Transístor-Transístor), que no geral utiliza transístores bipolares (BJT) NPN e PNP, e a tecnologia CMOS (Complementary Metal-Oxide Semiconductor / Metal-óxido Semicondutor Complementar), que usa Transístores de Efeito de Campo (FET) dos tipos MOSFET ou JFET.

Também podemos criar portas lógicas com a combinação de componentes eletrônicos discretos, como diodos, transístores e resistores, e até mesmo com relés, válvulas eletrônicas e dispositivos mecânicos.

As portas lógicas digitais são como blocos de construção básicos, com os quais são construídos circuitos eletrônicos digitais complexos, como microprocessadores, memórias de computador, circuitos de controle digitais, multiplexadores e muitos outros.

Estados Lógicos

Em lógica digital existem apenas dois estados permitidos (dois níveis de tensão elétrica), sendo denominados como nível alto (ligado) e nível baixo (desligado), 1 e 0, ou ainda, Verdadeiro e Falso. Representamos esses estados lógicos em álgebra booleana por meio dos valores binários 1 e 0.

Há duas formas de representar esses níveis lógicos por meio de um circuito digital:

- Lógica Positiva: O nível lógico 0 (ou baixo / low) é representado eletricamente por uma tensão de zero volts (na prática, próxima a zero volts), e o nível lógico 1 (ou alto / high) é representado por uma tensão elétrica mais alta, como por exemplo 5 volts.

- Lógica Negativa: Os níveis lógicos são inversos em relação à Lógica Positiva. Esse tipo de lógica é muito pouco empregada, por isso vamos utilizar em nosso curso sempre as noções de lógica positiva.

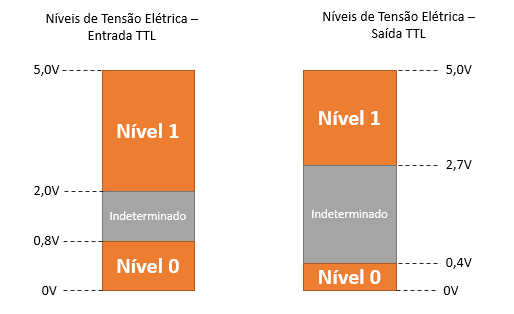

É interessante notar que, quando usamos circuitos que implementem a tecnologia TTL, os estados lógicos são dados por intervalos de valores de tensão elétrica, e não valores específicos em si. A figura a seguir mostra os níveis lógicos de entrada e saída comuns (e aceitáveis) em um circuito TTL típico:

Níveis de Tensão Elétrica em Lógica TTL

De acordo com a figura, ao usarmos um dispositivo lógico construído com tecnologia TTL, uma tensão elétrica entre 2,0V e 5,0V é considerada como um nível lógico 1 (ALTO), ao passo que uma tensão elétrica abaixo de 0,8V é considerada como um nível lógico 0 (BAIXO). Já a tensão elétrica entre 0,8V e 2,0V é uma região indeterminada, não representando nem o nível 0 nem o nível 1, e portanto devemos evitar que o circuito opere nessa região, para que não sejam produzidos valores de saída errôneos / falsos.

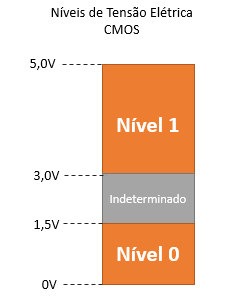

A seguir temos uma figura que traz os níveis lógicos e suas respectivas tensões elétricas utilizadas em tecnologia CMOS padrão:

Níveis de Tensão Elétrica em um dispositivo CMOS

Os níveis apresentados na imagem correspondem aos valores de tensão de entrada aceitáveis em um dispositivo CMOS típico, sendo que a tensão elétrica pode, na verdade, ser maior do que 5V (os dispositivos CMOS suportam até 18 VDD na entrada). A saída deve ser de no máximo 0,05V para o nível 0 (baixo) em tecnologia CMOS, e entre 4,95 e 5V para o nível 1 (alto).

Idealmente, para qualquer circuito digital, os níveis de tensão que representam os valores lógicos 0 e 1 deveriam ser, respectivamente, de 0V e 5V; porém, isso é muito difícil de obter na prática, e por isso as tecnologias supracitadas possuem as faixas de valores aceitáveis para cada nível.

Com estas duas tecnologias, a TTL e a CMOS, são construídas as portas lógicas usadas nos mais diversos circuitos digitais existentes. As portas lógicas básicas são as portas AND, OR e NOT, mais as portas NAND, NOR, XOR e XNOR.

TTL ou CMOS?

Ao escolher entre as famílias de circuitos digitais TTL e CMOS para um projeto eletrônico, devemos levar alguns pontos em consideração, pois ambas possuem vantagens e desvantagens de uso:

- TTL: Uma de suas principais desvantagens é o fato de seu consumo elétrico ser relativamente elevado, por serem construídos co transistores bipolares, que consomem uma boa quantidade de corrente elétrica. Além disso, as portas TTL possuem uma velocidade de operação limitada por conta desses transistores, o que significa que a transição entre um estado lógico 0 (Desligado / OFF) para um estado lógico 1 (Ligado / ON) leva um certo tempo, denominado Atraso de Propagação, o que pode causar impacto negativo caso haja necessidade de alta velocidade de chaveamento entre os níveis lógicos.

- CMOS: O consumo elétrico de dispositivos CMOS é muito mais baixo do que o dos dispositivos TTL, por serem baseados em tecnologia FET, estando na faixa de 1 a 2 microampères (1 a 2 uA)!. Assim, são ideais para uso em dispositivos nos quais o consumo elétrico seja um ponto crítico – tais como dispositivos portáteis, por exemplo. Uma outra vantagem dos dispositivos CMOS é seu baixo tempo de chaveamento, o que significa que a passagem de um nível lógico para outro se dá de forma muito rápida também.

Porém, os circuitos CMOS possuem uma desvantagem que deve ser levada em consideração: eles são danificados com muita facilidade por eletricidade estática. Por isso, devem ser protegidos contra descargas que possam afetar os circuitos onde se encontram, e também ao serem manuseados, pois os circuitos integrados CMOS são muito sensíveis, e podem se danificar até mesmo com um simples contato com as mãos do técnico que os manipula. Usar uma pulseira anti-estática é uma boa ideia nesse caso.

Simbologia

Existem dois conjuntos de símbolos para representar as portas lógicas, ambos definidos pelo padrão ANSI/IEEE Std 91-1984 e seu suplemento, o ANSI/IEE Std 91a-1991. O primeiro conjunto, cujos símbolos possuem formatos distintos para cada porta lógica, é mais utilizado em desenhos simples, e às vezes conhecido como “padrão militar’, devido ás suas origens. Já o segundo conjunto, refinado pelo IEC e batizado de padrão IEC 60617-12, com formatos retangulares dos símbolos, permite a representação de uma quantidade muito maior de dispositivos do que é possível usando a simbologia tradicional.

Em nossos tutoriais iremos sempre mostrar ambos os símbolos, de modo que você será capaz de desenhar e entender qualquer diagrama de circuito lógico apresentado.

Na próxima lição iniciaremos o estudo individual das portas lógicas citadas anteriormente. A primeira a ser estudada é justamente a porta lógica mais simples – a Porta NOT (inversora).

Escreva um comentário